#### Agenda

Software → FPGA → ASIC

Lower Latency and Stay Nimble

ASIC Flow, Investment, Trade-offs

Decision Approach and Next Steps

#### Financial Analytics Evolution

ASIC to support faster ethernet and enable edge intelligence

HPC Custom Drivers ASIC Updateable Accelerator Analytics

FPGA to reduce packet latency and enable edge computing

HPC Custom Drivers

FPGA Accelerator

Driver SW to reduce packet latency

Financial SW / Big Data Analysis

High-Performance Compute (HPC)

cādence

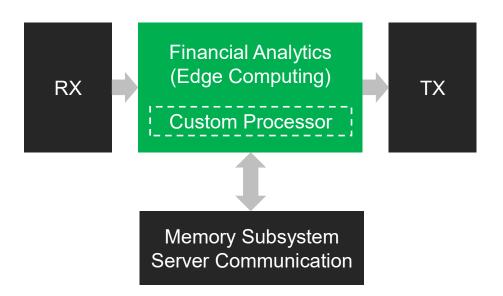

#### FPGA to ASIC: Gain Performance Potential to Remain Nimble

- ASIC removes system latency

- Faster RX/TX ethernet

- Faster memory subsystem

- Opens performance tuning options

- Push more analytics to edge computing

- Push more data to server analytics

- ASIC can also be nimble

- Custom processor SW programmable with unique instructions for low-latency

- eFPGA potential for reconfigurable logic

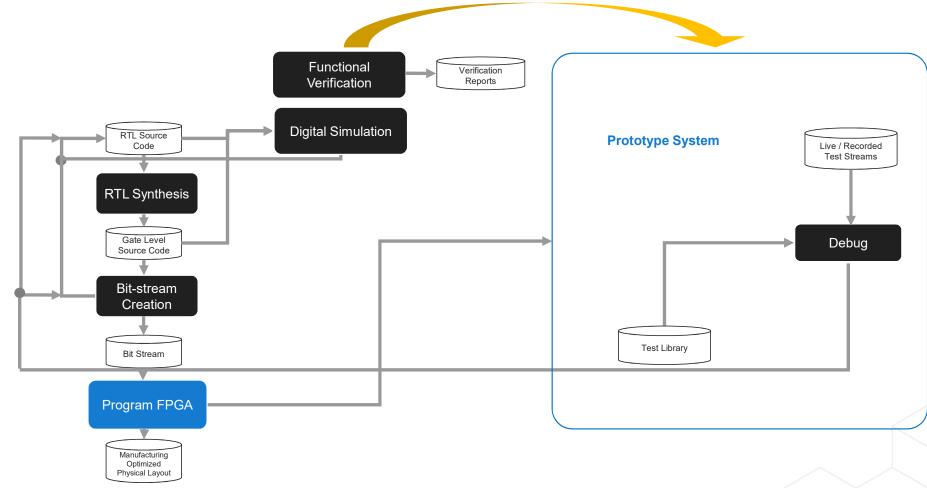

#### High-Level FPGA Development Flow

RTL Coding And Synthesis

Simulation

FPGA Programming (Physical Implementation)

Hardware Testing

And

Debug

### Detailed FPGA Development Flow

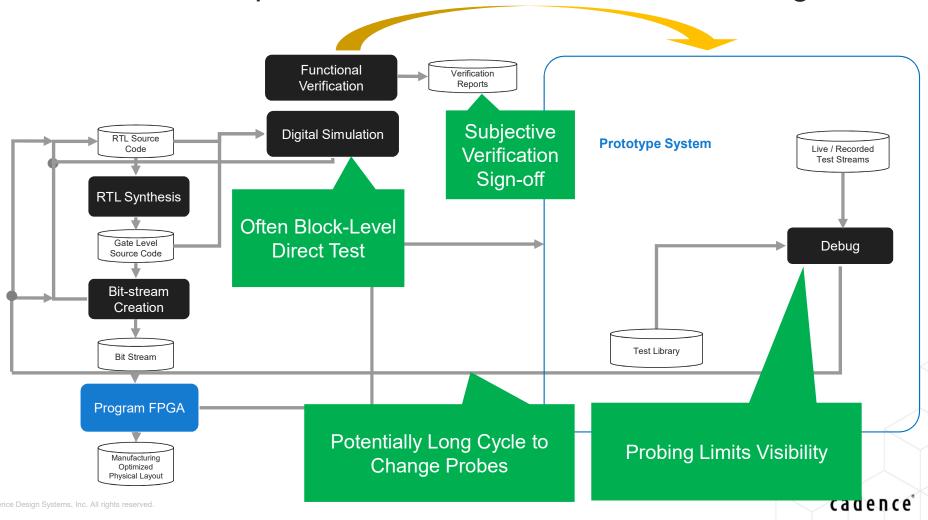

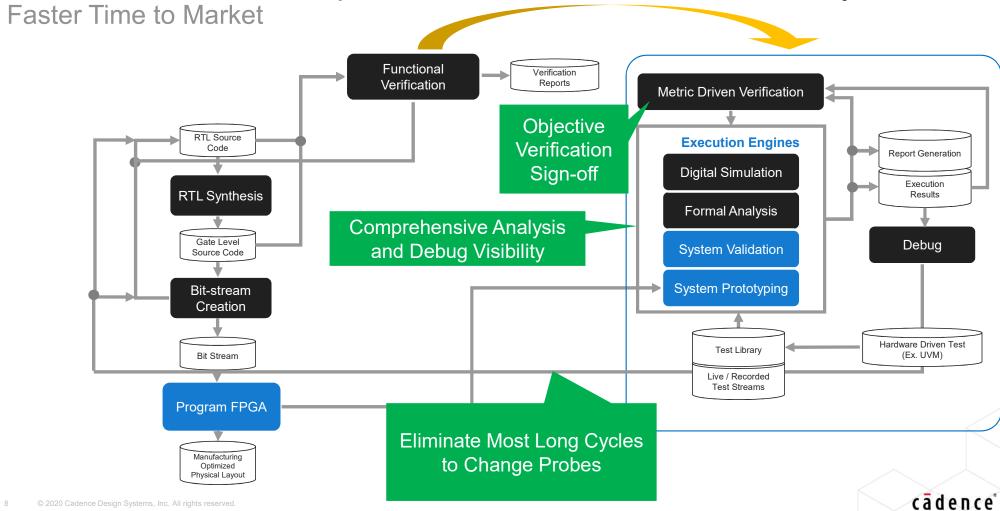

#### Detailed FPGA Development Flow With Verification Challenges

Detailed FPGA Development Flow With Quantitative Analysis

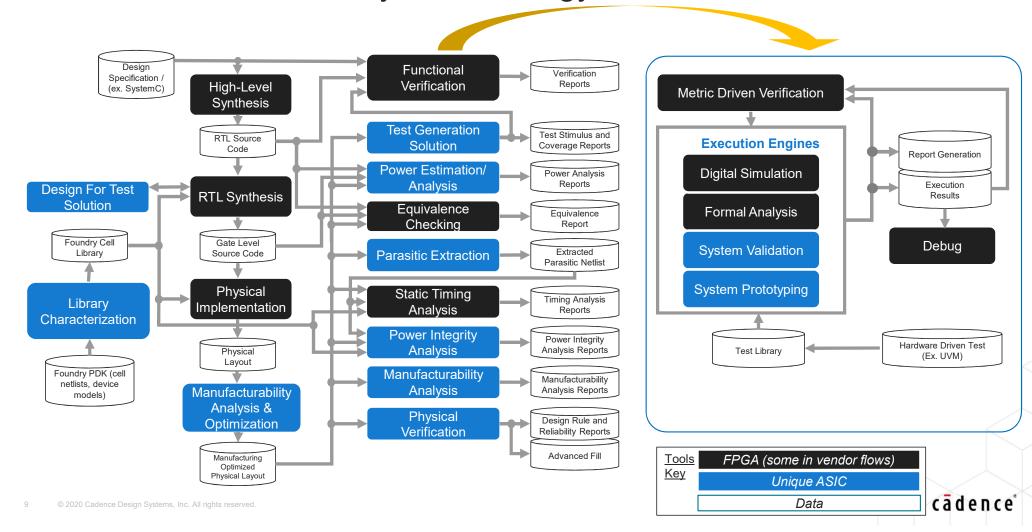

#### ASIC Flow Adds Foundry Methodology and Tools

#### High-Level ASIC Flow Adds Foundry Methodology and Tools

Many similarities to FPGA flow

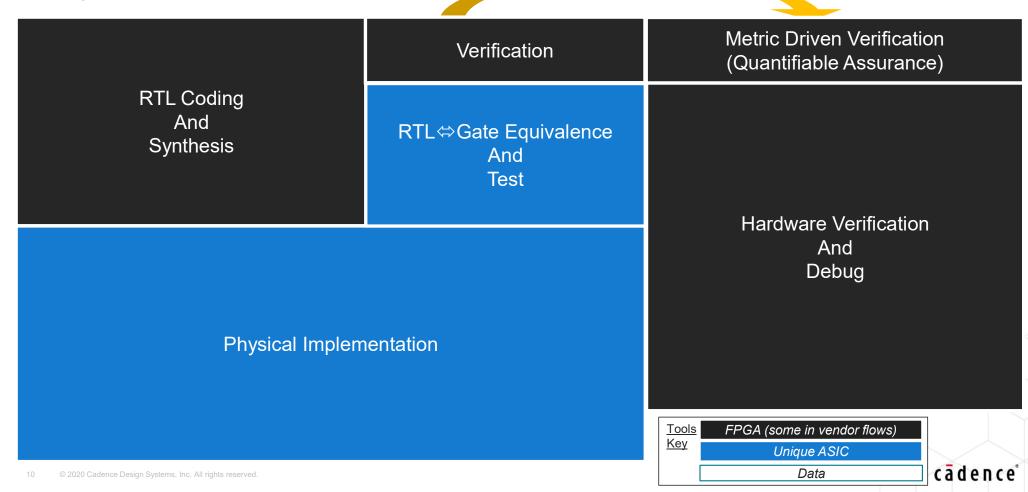

#### Focus on Application-Relevant Aspects of the Flow

Objective Verification of Design Features

Design to Achieve Performance Goals

RTL Coding And Synthesis Verification

RTL⇔Gate Equivalence And Test Metric Driven Verification (Quantifiable Assurance)

Hardware Verification

And

Debug

Physical Implementation

In-house or Service Provider to Assure 1<sup>st</sup> Pass Development Success Multi-point Verification to Assure 1<sup>st</sup> Pass Development Success

## Adapting FPGA Development for ASIC

| Flow Step         | Adaptation                                           | Engineering Skills                                                | Decision Processes                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------|------------------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IP                | New IP source(s) aligned to foundry and process node | Hire/consult with process knowledge                               | <ul> <li>Identify critical IP used in FPGA flow</li> <li>Evaluate custom processor to enable ASIC to be updated after production</li> <li>Research foundry and process node</li> <li>EDA provider and/or implementation service provider may have IP or be able to recommend</li> </ul>                                                                                              |

| Digital<br>Design | New synthesis and implementation tools               | New training for synthesis, hiring for implementation             | <ul> <li>RTL synthesis use similar to FPGA with new tools aligned to foundry and process node</li> <li>Determine if in-house implementation flow provides application-relevant differentiation; otherwise outsource</li> </ul>                                                                                                                                                       |

| Verification      | More exhaustive tool suite                           | New training and refocus from prototyping to tools; may grow team | <ul> <li>Start now! Faster time-to-market for FPGA with objective analysis of quality</li> <li>Shift toward verification automation is relevant for FPGA and ASIC due to growing complexity</li> <li>Verification skills differ from digital design such that additional training may not be sufficient</li> <li>Higher quality expectation may need additional resources</li> </ul> |

#### **ASIC** Concerns and Mitigation

ASICs are Fixed

- Focus fixed logic on communication architecture

- Proven configurable processor enables SW flexibility

- Emerging eFPGA can maintain HW flexibility

Time to Market is High

- Proven processes can execute in months

- Updateable IP maintains reactive retargeting

- Rigorous process tends to achieve better quality

Building Team is a Barrier

- Retraining and engineering resources available worldwide

- Staged hiring leveraging design and verification services

High Development Cost

- ROI from lower latency offsets development cost

- MPW runs in low (< 100) unit volume reduce foundry costs</li>

- Rigorous process offsets manual FPGA development costs

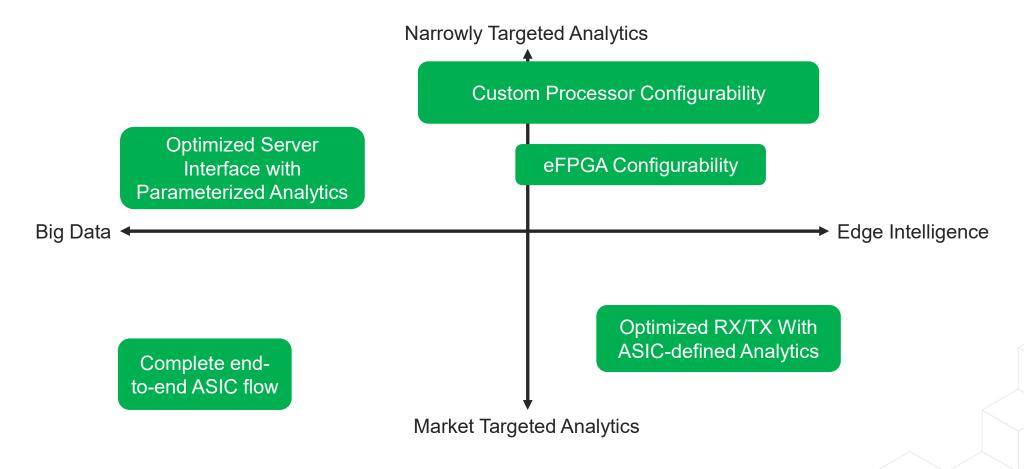

#### Implementation Path Defined By Financial Product Value Prop

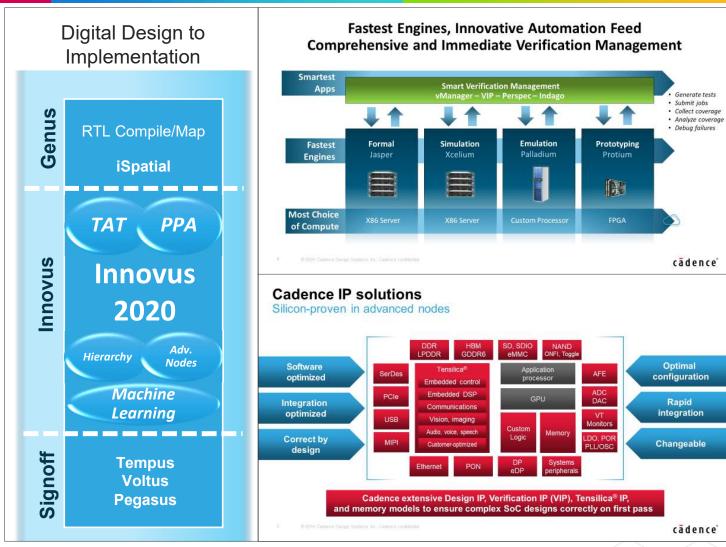

# Cadence is Your ASIC Partner

- Verification solution: apply objective analysis to improve FPGA and prepare for ASIC

- Link to Tech Brief

- ASIC solution: broadly adopted in high-speed comms and mission-critical applications

- Tensilica IP: proven processor technology used in autonomous drive and other high-reliability apps

- High-perf IP: proven in leading comms systems

- Services: expert RTL to GDS design services

© 2020 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo, and the other Cadence marks found at <a href="https://www.cadence.com/go/trademarks">www.cadence.com/go/trademarks</a> are trademarks or registered trademarks or logo. All rights reserved worldwide. Cadence Design Systems, Inc. Accellera and System and System are trademarks of Accellera Systems Initiative Inc. All Arm products are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All MIPI specifications are registered trademarks or service marks owned by MIPI Alliance. All PCI-SIG specifications are registered trademarks or trademarks or trademarks are the property of their respective owners.