# Accelerating time to first trade with FPGAs

Mark Eslinger Siemens EDA IC Verification Solutions / DVT

Restricted | © Siemens | STAC CI | October 2022

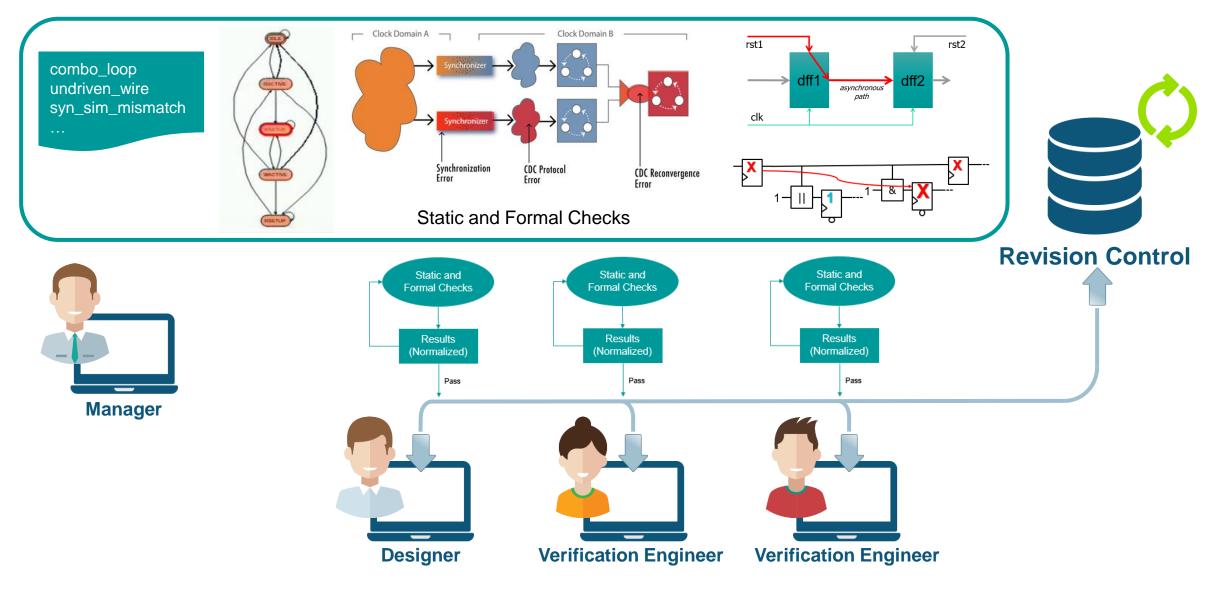

#### Applying agile/CI methods to h/w design with static and formal

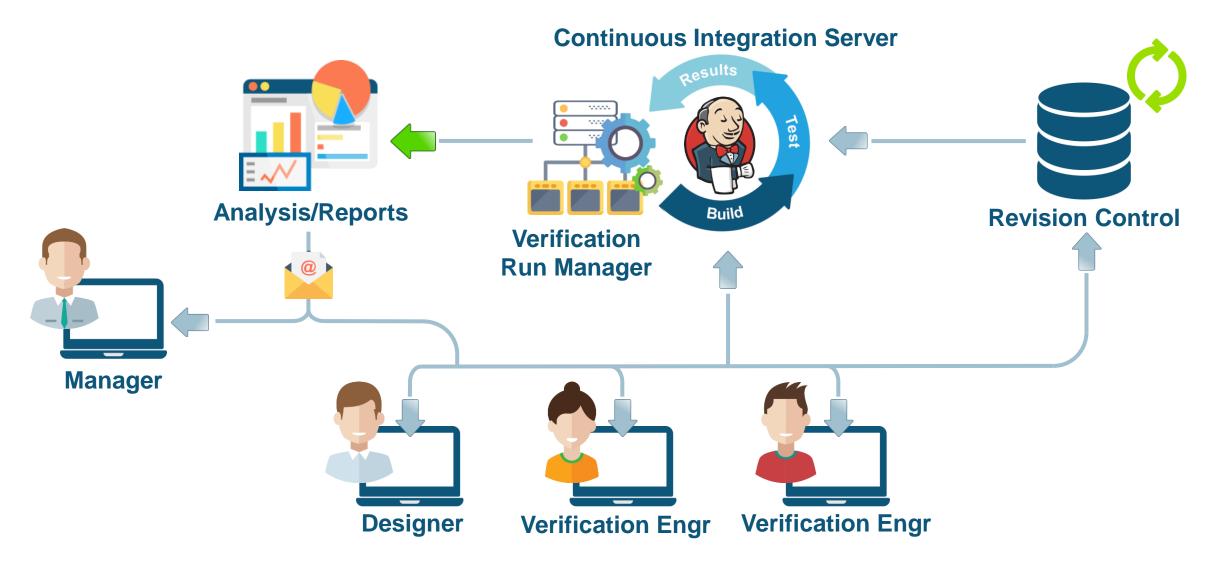

Continuous Integration (CI) is a development practice that requires developers to integrate code into a shared repository several times a day. Each check-in is then verified by an automated build, allowing teams to detect problems early.

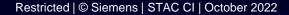

#### 84% of FPGA projects have non-trivial bug escapes

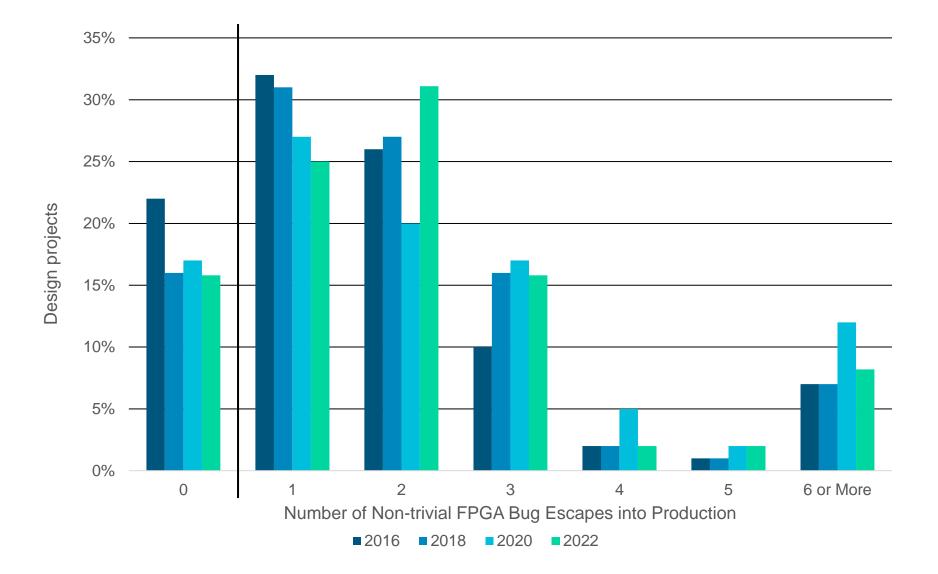

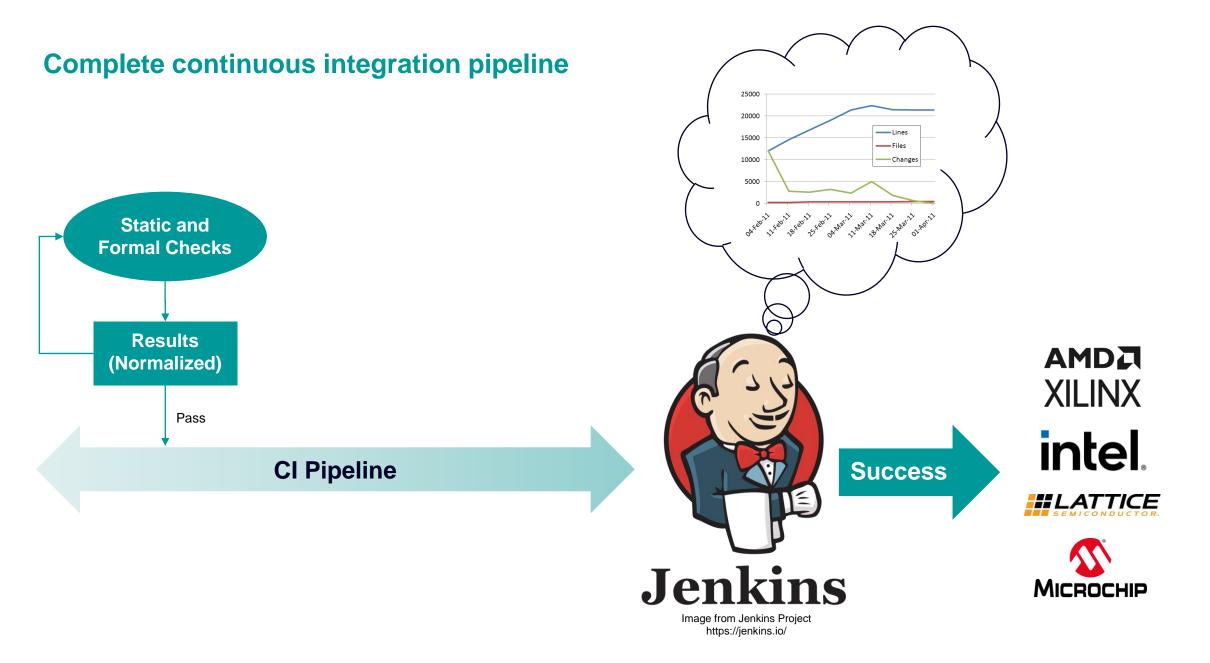

#### Static and formal design checks build a continuous integration pipeline

#### Team based early functional verification tied to CI flows

#### **Example: Comparing lint and formal lint**

#### Lint?

No – this is not Lint

Syntax checks: ✓

Semantic checks: ✓

Structural checks: ✓

Stylistic checks: ✓

```

case (qstate)

3'b001: if (en) dstate = 3'b010;

else dstate = 3'b001;

3'b010: dstate = 3'b100;

3'b100: if (rtn) dstate = 3'b001;

else dstate = 3'b100;

default: dstate = 3'b001;

endcase

```

#### **Formal Lint?**

#### Yes! It's Formal Lint

#### **Sequential checks:**

- Understands whether **rtn** can ever be 1.

- If not, the FSM will deadlock at state 3'b100.

Advanced Linting checks beyond static checks

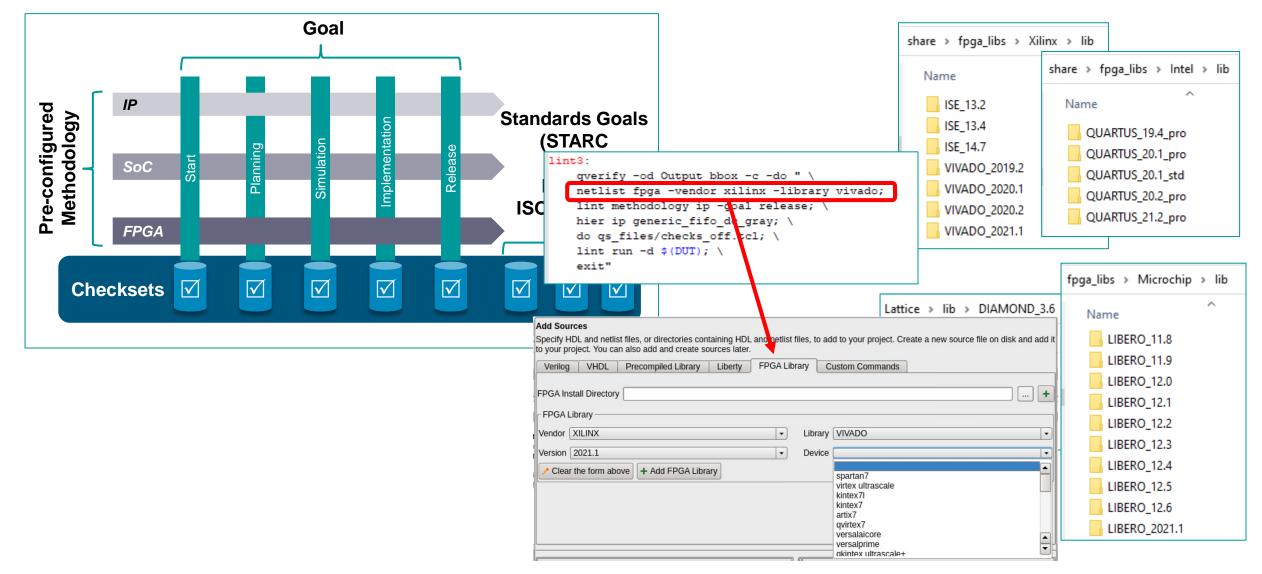

#### FPGA methodologies and library support to enhance value of a CI flow

#### **Build and test using CI**

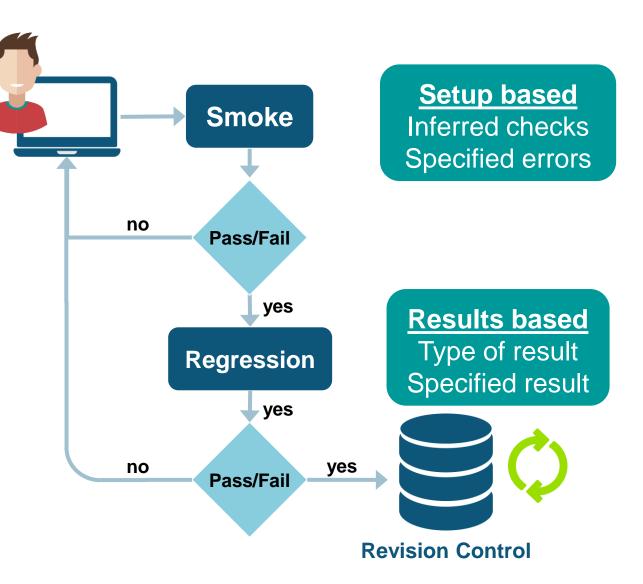

#### **Trunk check**

- Sanity test

- Subset of regression

- Detect simple yet severe problems

- Frequency

- Ran at least daily on trunk

- Before every check-in

#### Regression

- Full test of functionality

- Verify implemented features

- Adds coverage

- Frequency

- Ran at most nightly

#### Automating Verification: Providing productivity and efficient use of resources

#### **Typical Regression Limitations**

- No alternative but to home grow

- Script based, little separation between configuration and control

- Expensive to create & maintain

- Hidden data & automation opportunities

#### Benefits of a pre-built environment

- Focus resources on verification, not infrastructure

- Simplify set-up & Maintenance

- Continual development & support

#### Improve throughput and turn-around

- Faster execution of regression tasks

- Automation and repeatability of process

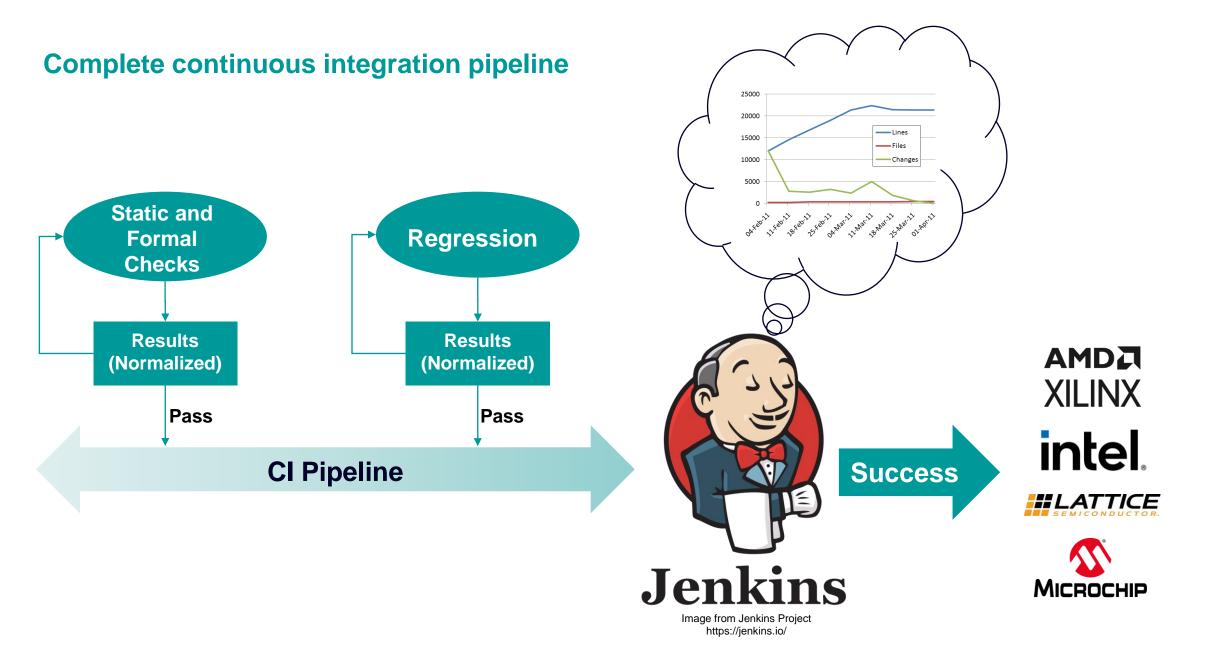

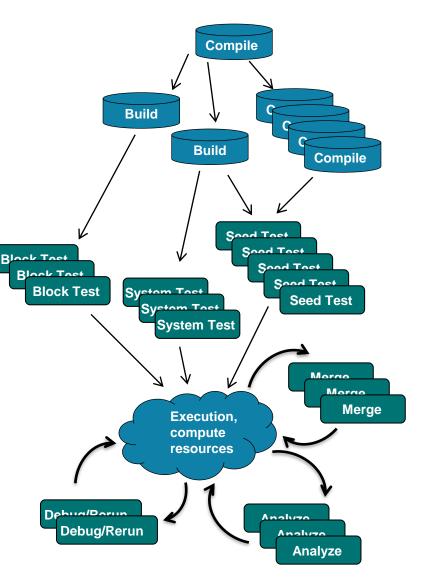

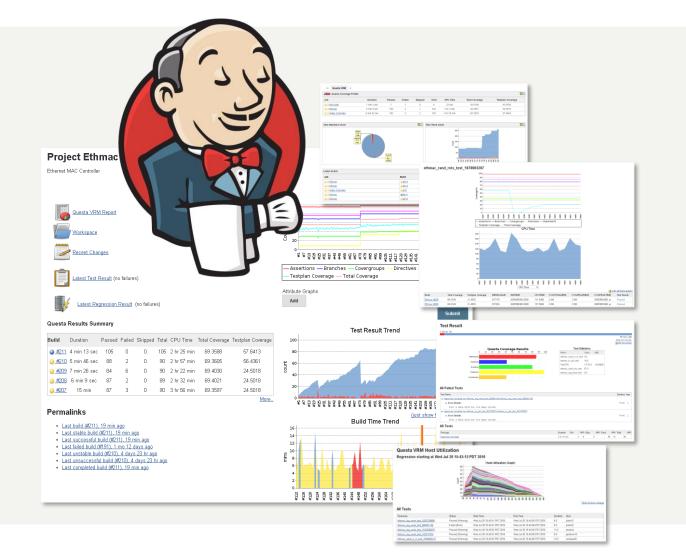

#### **Regression Management and Continuous Integration** Run Management Plug-in for Jenkins

#### **Verification Automation**

- Continuous Integration

- Run Management

#### **Improved Quality**

- Frequent Testing

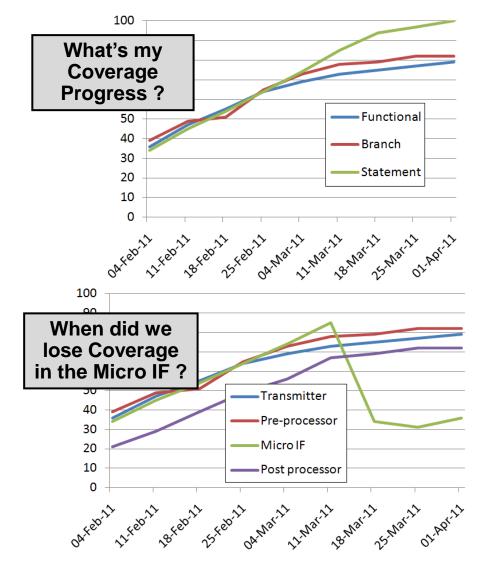

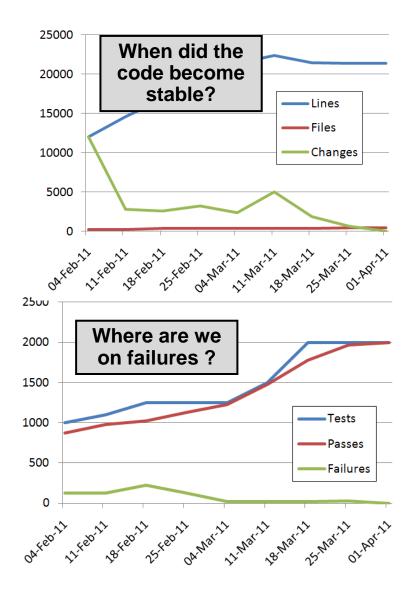

- Faster Coverage Closure

#### **Process Collaboration**

- Results Analysis

- Metric Visualization

#### **Powerful analysis** *Who, What, When, Where, Why?*

#### **Complete regression flow**

Once intent is proven, ensure it is never broken with continuous integration Run tools early and often to gain time-of-error insight

#### Integrate analyses into continuous integration flows

- Protect from faulty check-ins

- Protect from conflict errors

#### Build increasing rigor of checks into build stages

- Light high-value checks for check-ins

- Deeper checks prior to daily and weekend regressions

- Deepest checks prior to emulation/prototyping builds

### **Continuous Integration**

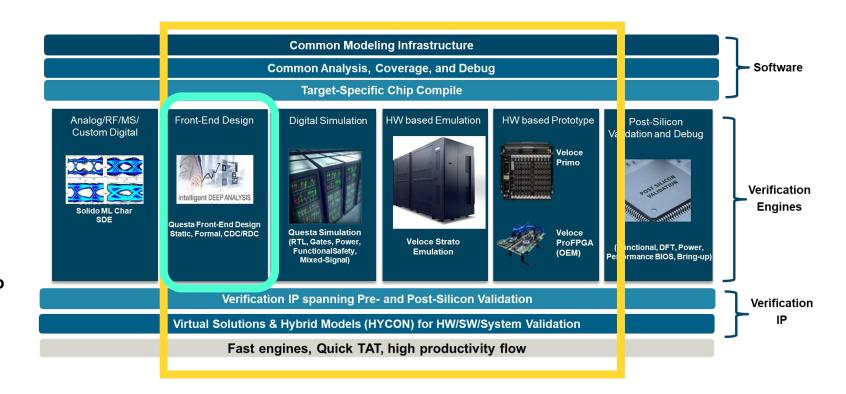

#### **Siemens DVT's Enterprise Verification Platform components**

#### **Verification engines**

- Questa Simulation

- Questa Formal

- Veloce HW-Assisted Verification

#### **Platform technologies**

- Questa Visualizer Debug

- Questa Verification IQ Coverage

- Portable Stimulus / Verification IP

#### **Extended verification**

- Questa Design Solutions

- Functional safety

- Cloud solutions

Questa Lint, AutoCheck, X-Check, CDC, RDC

SIFMENS

#### **Disclaimer**

© Siemens 2022

Subject to changes and errors. The information given in this document only contains general descriptions and/or performance features which may not always specifically reflect those described, or which may undergo modification in the course of further development of the products. The requested performance features are binding only when they are expressly agreed upon in the concluded contract.

All product designations may be trademarks or other rights of Siemens AG, its affiliated companies or other companies whose use by third parties for their own purposes could violate the rights of the respective owner.

## Contact

Published by Siemens 2022

Mark Eslinger Questa Design Solutions Product Manager DVT (IC Verification Solutions)

E-mail: mark.eslinger@siemens.com