# **STAC Update for Fast Data**

Peter Lankford Founder and Director, STAC

peter.lankford@STACresearch.com

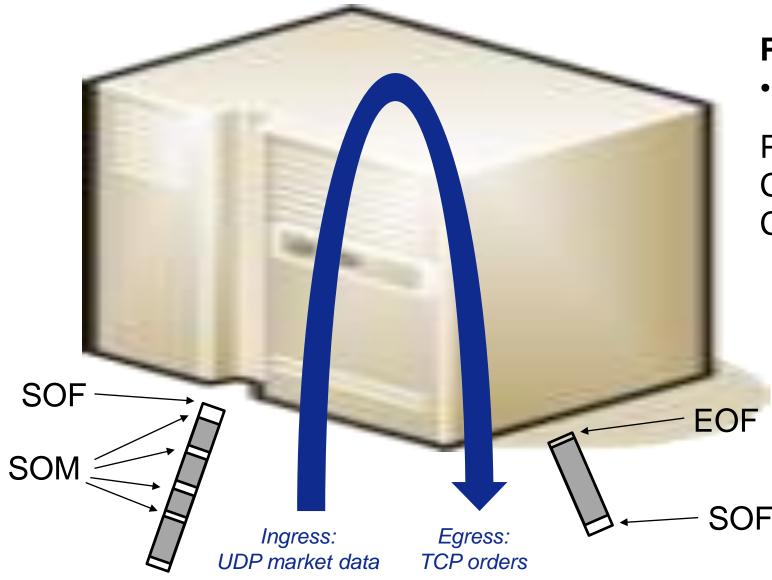

## STAC-T0 vs STAC-T1

- Both are a tick-to-trade pattern

- UDP in

- TCP out

- Both use wire timestamps

- High accuracy

- Work with any trading platform (sw/hw)

- STAC-T1 includes protocol handling

- Market data decoding

- Order encoding

- STAC-T0 does not

- No market-specific logic

- Isolates network I/O latency

## Quick review: Latest STAC-T0 results

- Finalized and published Exablaze STAC-T0 results

- Refined the calculation of inferred timestamps (sub-ns impact)

- Matt Grosvenor will describe some of the complexities shortly

- New high ingress rates tested:

- 1.9 M packets/sec (7.7 Gbps) for 507B frames

- 11 million packets/sec (6.2 Gbps) for 68B frames

- Set new records in every measurement

- Over 50% lower latency than previous records

Across <u>all</u> message sizes and <u>all</u> message rates, Actionable Latency:

- Max of ~44 nanoseconds (STAC-T0.β1.\*.\*.ACTIONABLE.MAX)

- Min of ~31 nanoseconds (STAC-T0.β1.\*.\*.ACTIONABLE.MIN)

www.STACresearch.com/EXA181106

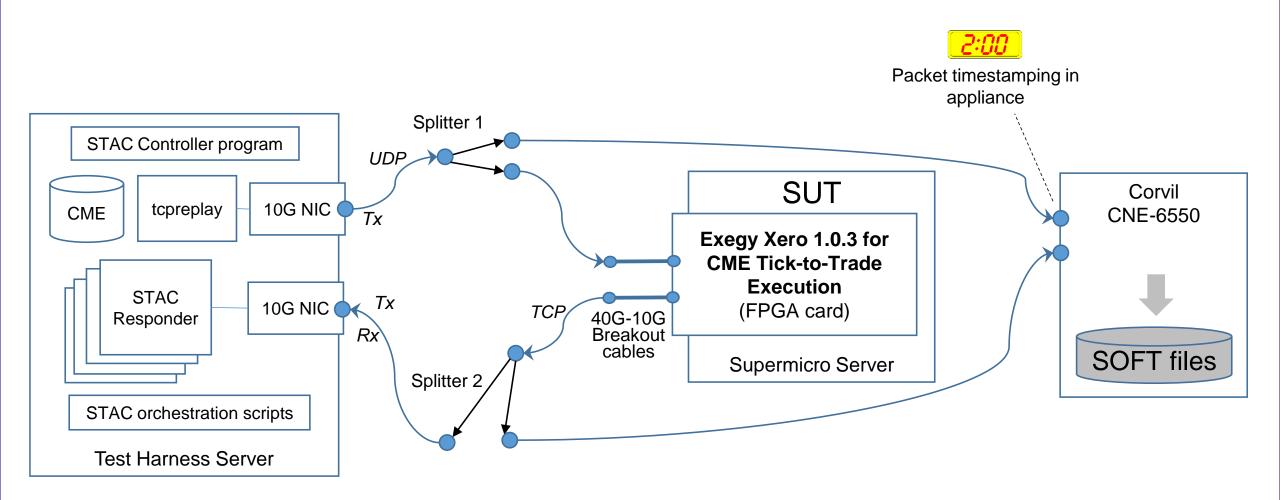

## Exegy under STAC-T1.EMINI

- Tested Exegy Xero 1.0.3 for CME Tick-to-Trade Execution

- FPGA card

- First we had to bring STAC-T1.EMINI up to date

- Updated to latest CME market data protocol (MDP 3.0)

- Dataset is now a recent quadruple witching day

- Increased the set of latencies reported

- Because market data is different, these results <u>cannot</u> be fairly compared to previous STAC-T1 results

#### Latencies

#### **Previous STAC-T1.EMINI:**

SOF(in) to EOF(out)

Pro: complete latency picture Con: includes serialization delay Con: not useful for algos that wait for mkt data messages

### Updated STAC-T1.EMINI:

Above, plus -

- SOF(in) to SOF(out)

- SOM(in) to SOF(out)

- SOM(in) to EOF(out)

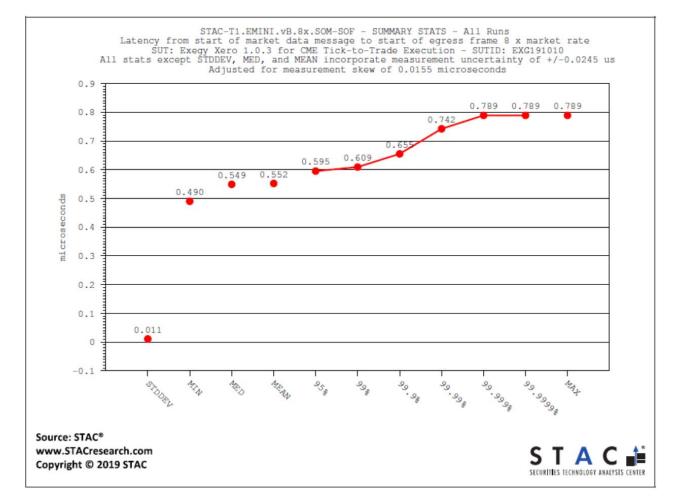

### STAC-T1.EMINI.vB.1x.SOM-to-SOF STAC-T1.EMINI.vB.8x.SOM-to-SOF

At both 1x and 8x market rate, the latency from the start of the market data message to the start of the order frame was:

- 0.552 microseconds (MEAN)

- 0.609 microseconds (99P)

- 0.789 microseconds (MAX)

- 0.011 microseconds (STDEV)

SECURITIES TECHNOLOGY ANALYSIS CENTER

## "STAC MAC"

- Business context: There's a market for MAC/PHY IP cores

- Purpose of the benchmark: measure the performance of vendorprovided MAC and PHY for a given FPGA chip

- Started with a proposal from Matt Grosvenor (Exablaze):

<u>www.STACresearch.com/STAC-Summit-13-Jun-2018-exablaze</u>

- Olivier Baetz developed a very detailed proposal

## "STAC MAC" continued

- Has gotten a lot of valuable discussion in the STAC online forums

- Have crystallized the key debating points

- Debate to happen by telecon this quarter

- Sign up to be involved: <u>www.STACresearch.com/nio</u>

#### Get access to this domain

If you'd like to obtain privileged materials from this domain, or if you would like to participate in this group, please click the button below.

Enable me! >