#### Demystifying FPGA Design and Verification

Harry D. Foster

Chief Scientist Verification Design Verification Technology

June 5, 2017

#### THE ERA OF DIGITAL INTELLIGENCE

#### **Everything Connected and in the Cloud**

| <b>Mo</b><br>World                 | re Cor      | nnected De                                             | vices Tha                                                               | an People       |                            |         |              |             |

|------------------------------------|-------------|--------------------------------------------------------|-------------------------------------------------------------------------|-----------------|----------------------------|---------|--------------|-------------|

| Population                         | 6.3 Billion | 6.8 Billion                                            | 7.2 Billion                                                             | 7.6 Billion     |                            |         |              |             |

|                                    | ŵ.          | IBM Investor Briefing                                  |                                                                         |                 |                            |         |              |             |

|                                    |             | Smarter Planet describes the emerging era of computing |                                                                         |                 |                            |         |              |             |

| Connected<br>Devices               | 500 Mil     | Instrum .                                              | Evans, CTC                                                              | D of Stringify, | says <mark>30 billi</mark> | on coni | nected devic | ces by 2020 |

|                                    |             | Intercor •                                             | Ericsson fi                                                             | gures on 28     | oillion by 202             | 20      |              |             |

| Connected<br>Devices<br>Per Person | 0.08        | Intellig                                               | <ul> <li>HIS Markit projects 30.7 billion IoT devices by2020</li> </ul> |                 |                            |         |              |             |

|                                    |             | •                                                      | Cartner ex                                                              | pects 20.8 bi   | llion by 2020              | )       |              |             |

|                                    |             | • IDC anticipates 28.1 billion by 2020                 |                                                                         |                 |                            |         |              |             |

LOW Latency

FPGA-Based Acceleration

#### **REALLY BIG DATA & FAST DATA**

High Availability

Real-Time Compute

Machine Learning

Security

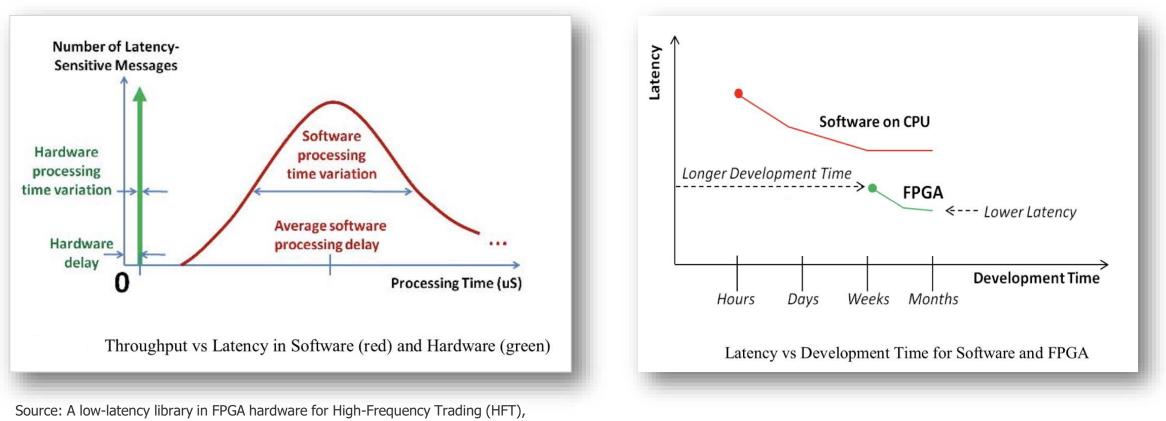

#### **Advantages of FPGA-Based Accelerator Platforms**

Competitive Advantage Through Low Latency and Faster Compute

2012 IEEE 20th Annual Symposium on High-Performance Interconnect

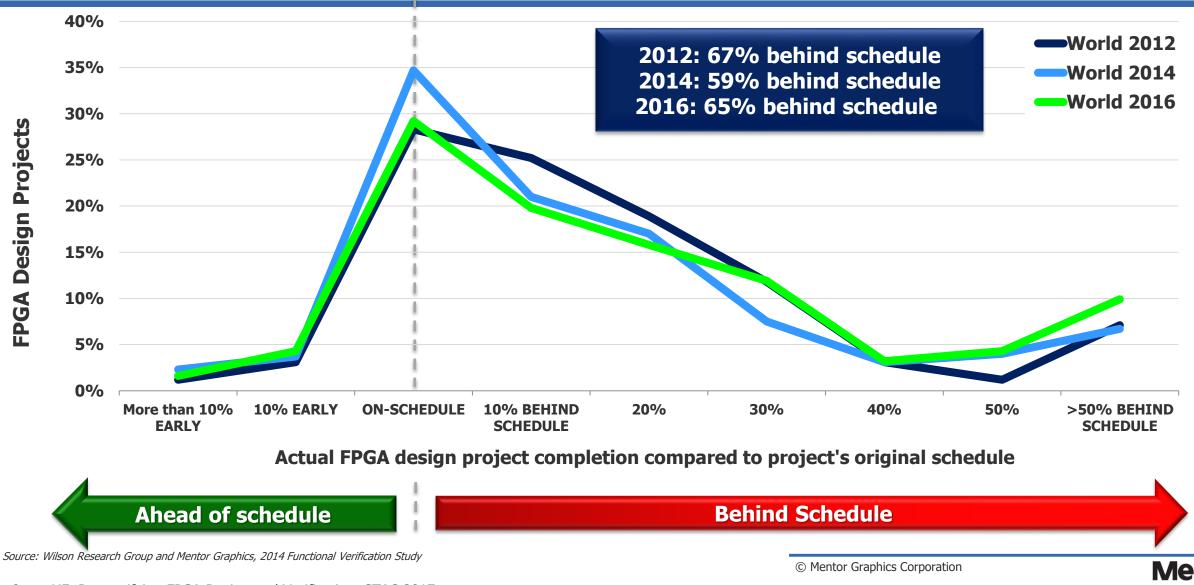

#### **The Need to Shift Left**

Characteristics of Projects Who Meet or Exceed Schedule

6 HF, Demystifying FPGA Design and Verification, STAC 2017

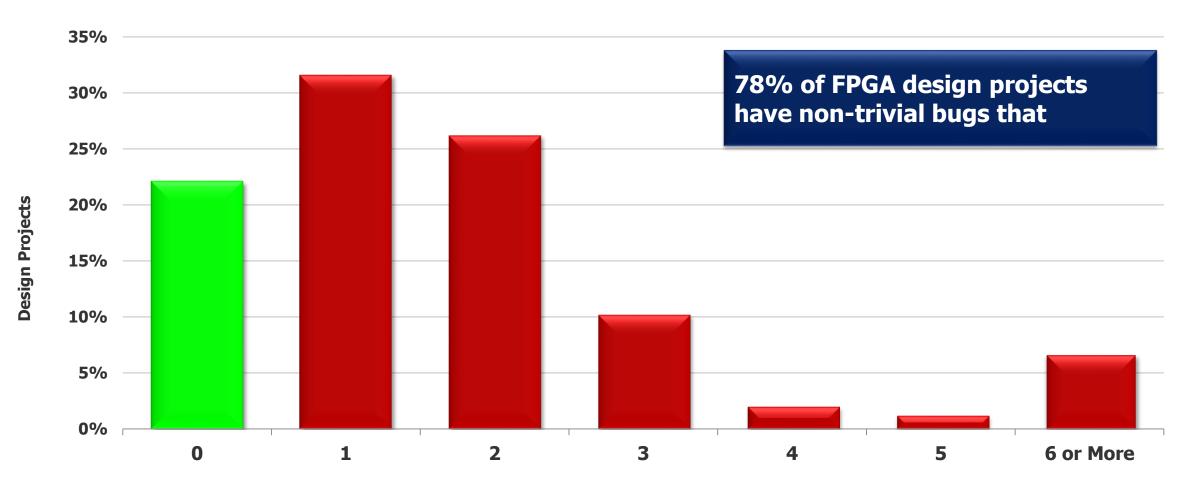

#### The Need to Be Green

Characteristics of Projects Without Bug Escapes

#### **2016 FPGA Non-Trivial Bug Escapes to Production**

Source: Wilson Research Group and Mentor Graphics, 2016 Functional Verification Study

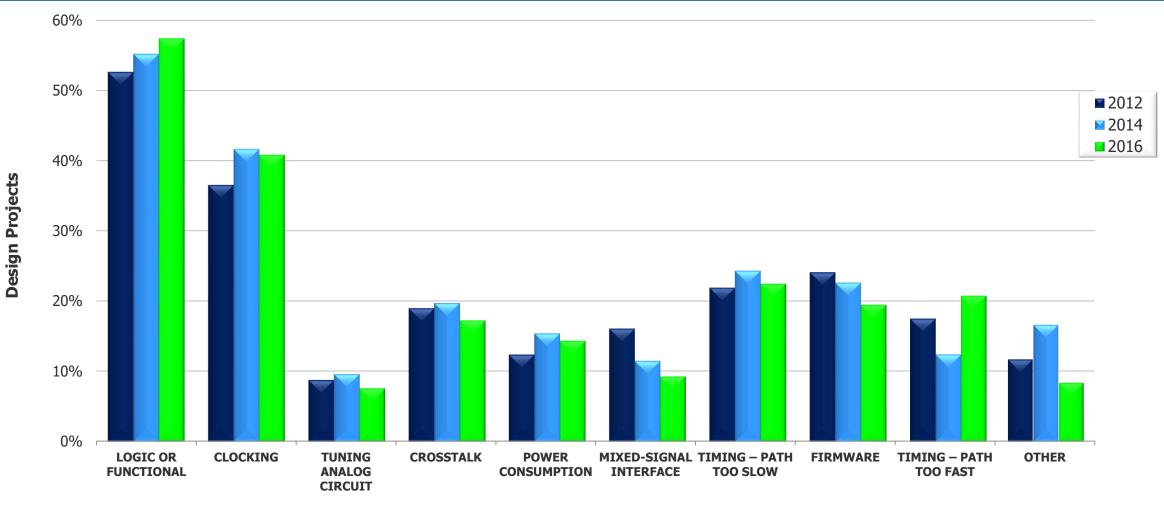

#### **Flaws Contributing to FPGA Rework**

**Trends in Types of Flaws Resulting in Rework**

\* Multiple answers possible

Source: Wilson Research Group and Mentor Graphics, 2016 Functional Verification Study

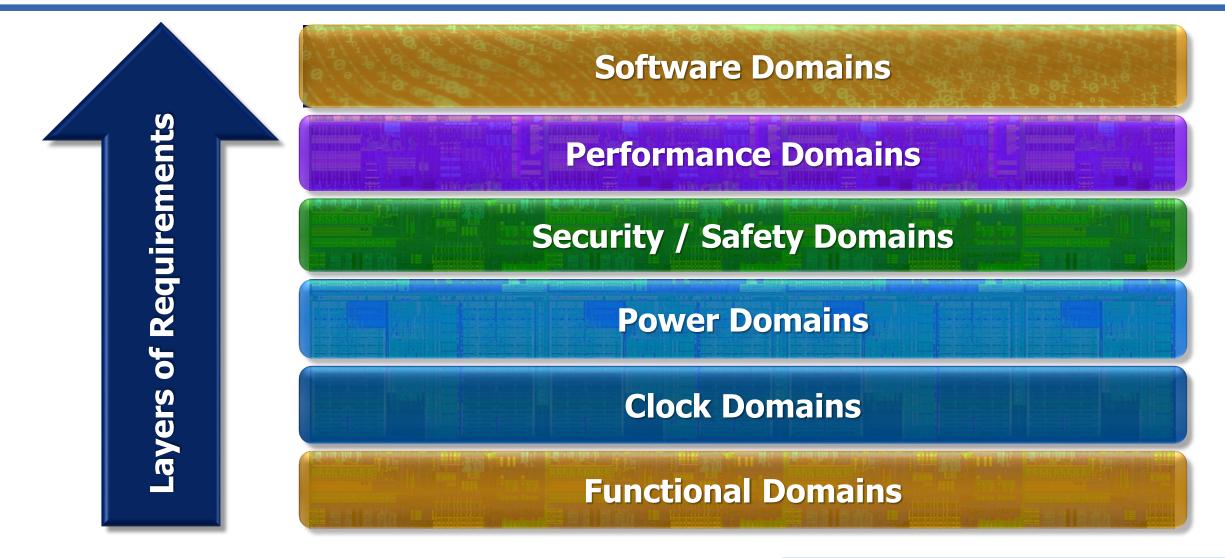

#### **RISING VERIFICATION COMPLEXITY**

#### The Emergence of New Layers of Verification Requirements Brought on by the System Era

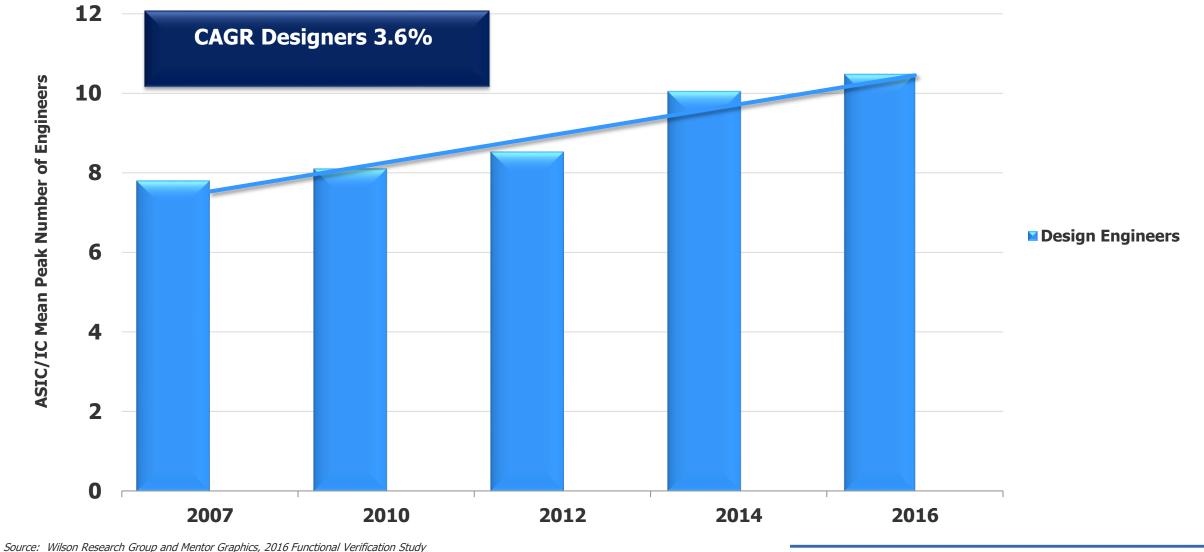

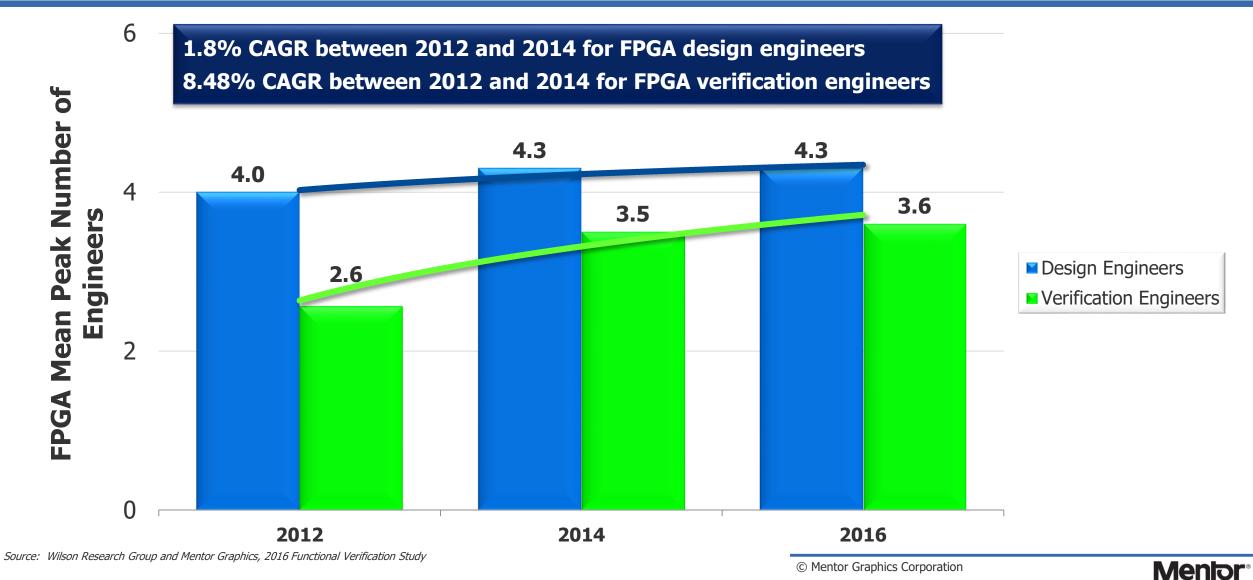

#### **Demand for Design Engineers Grows Slowly**

11 HF, Demystifying FPGA Design and Verification, STAC 2017

<sup>©</sup> Mentor Graphics Corporation

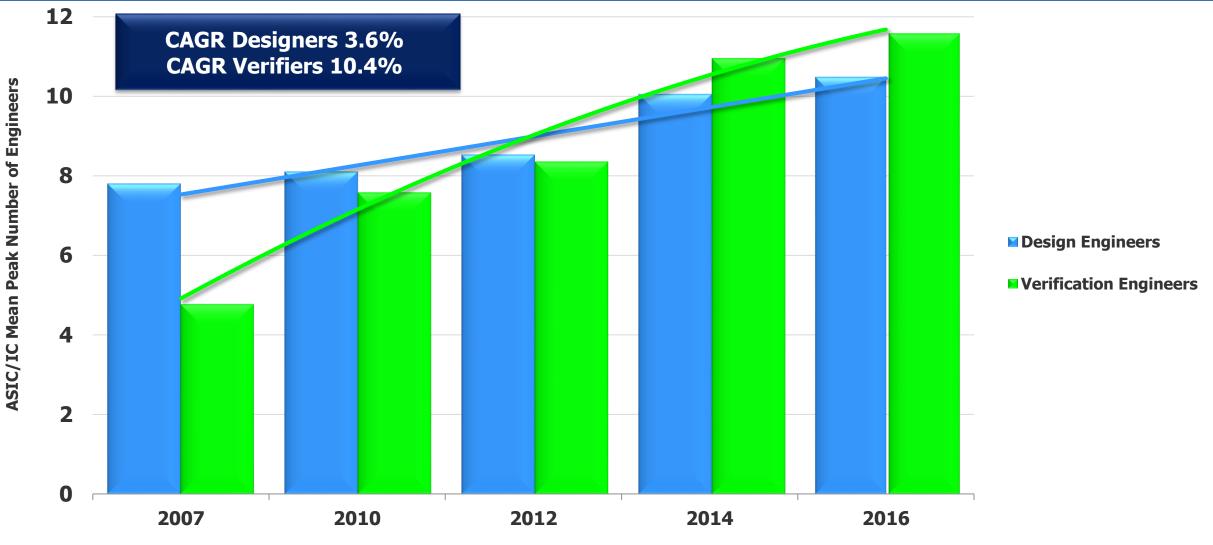

#### **But what about Verification Productivity?**

© Mentor Graphics Corporation

Mento

Source: Wilson Research Group and Mentor Graphics, 2016 Functional Verification Study

#### About a 1-to-1 Ratio of FPGA Verification and Design Engineers

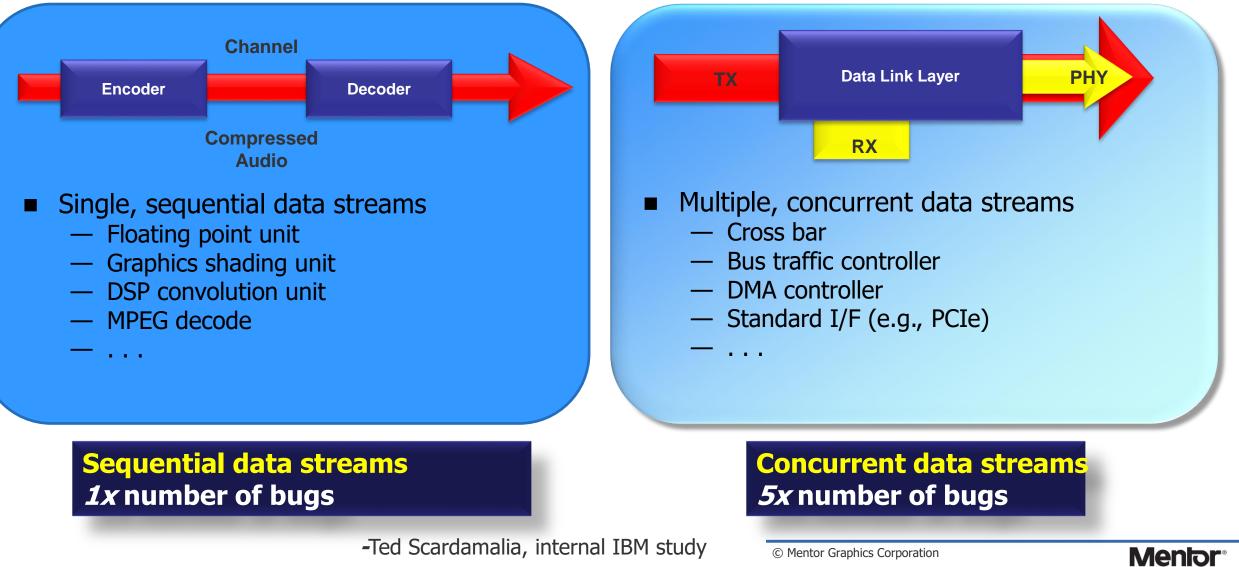

#### What Makes Functional Verification Difficult?

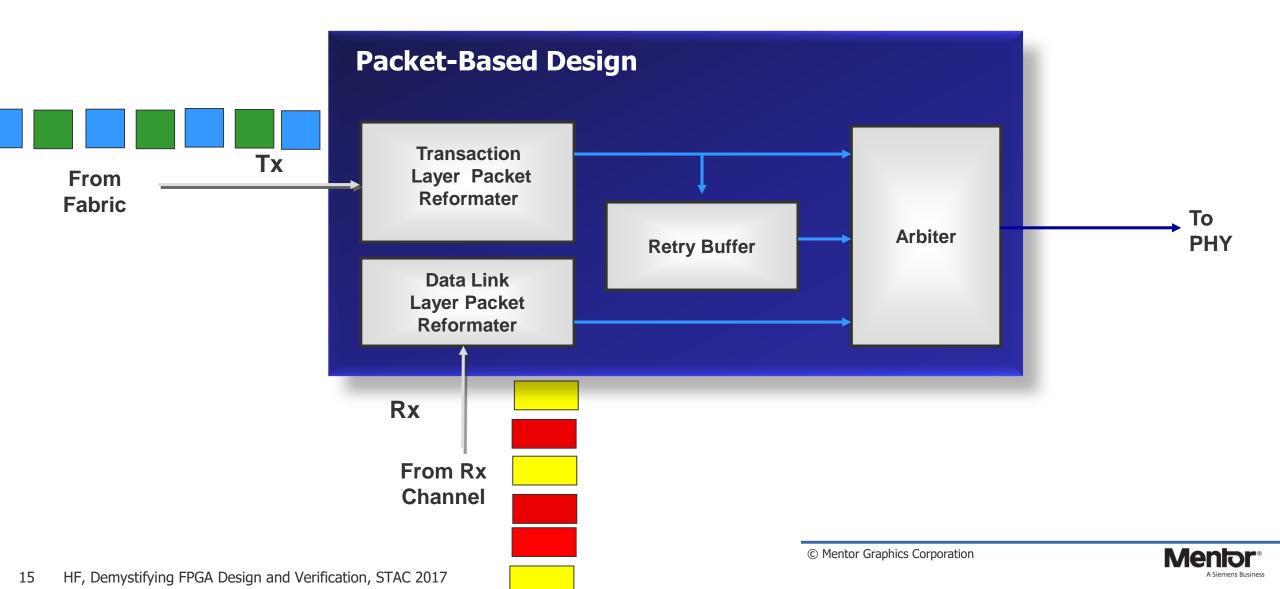

#### **Verifying Concurrency Requires Appropriate Solutions**

#### **Finding Corner Case Bugs Requires Appropriate Solutions**

## Directed-test-based simulation finds the bugs you can think of...

## Constrained-random simulation finds the bugs you never anticipated!

16 HF, Demystifying FPGA Design and Verification, STAC 2017

#### **VERIFICATION BEST PRACTICES**

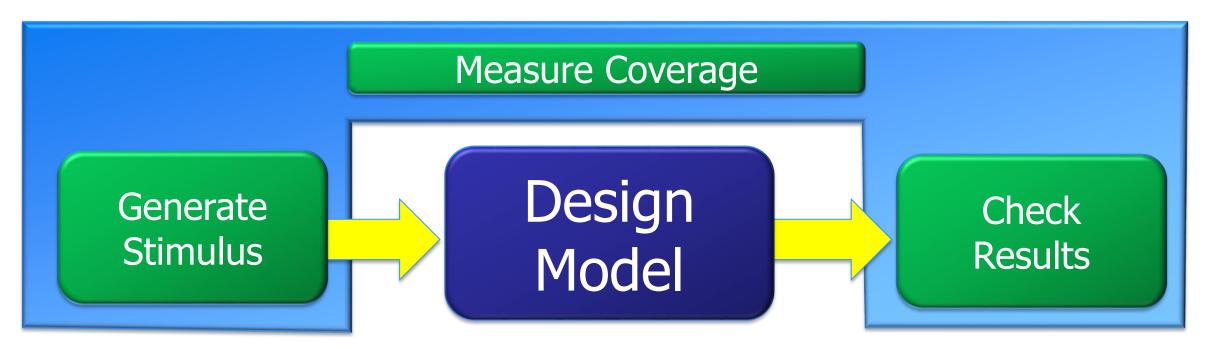

#### **Simulation-Based Techniques**

- Fundamental verification technique in use today

- Generally scales well

- Testing all possible states is generally incomplete

Assertions can be used to check results and measure coverage

© Mentor Graphics Corporation

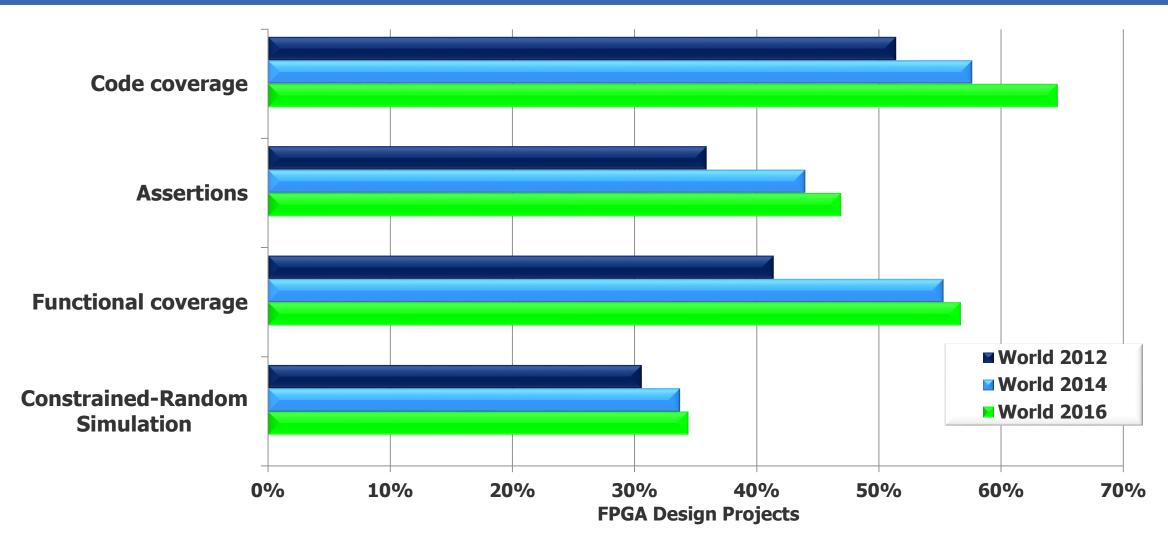

#### **FPGA Projects are Maturing their Verification Processes**

Source: Wilson Research Group and Mentor Graphics, 2016 Functional Verification Study

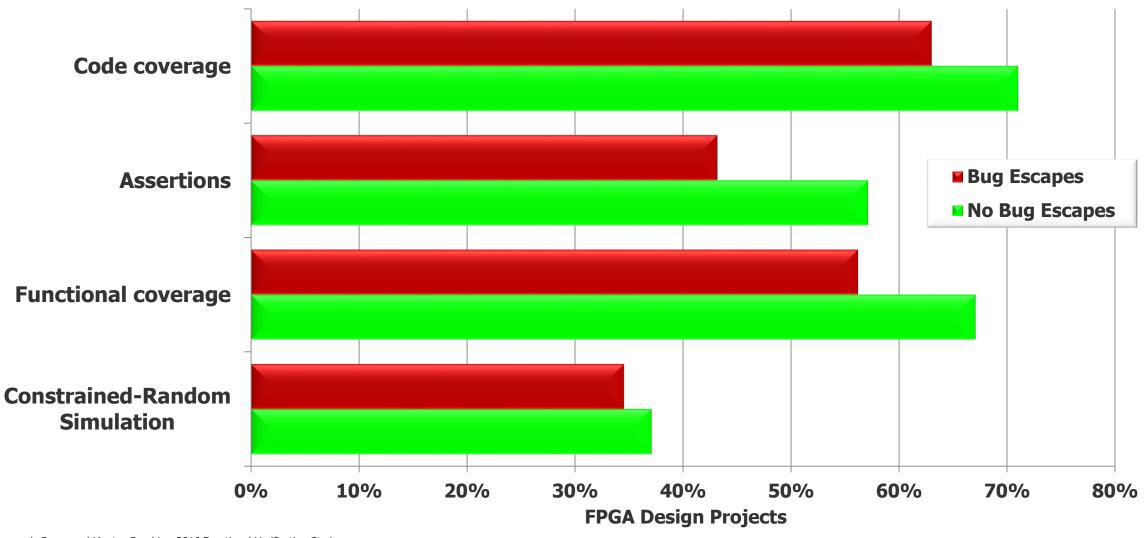

#### **FPGA Verification Technology Adoption and Bug Escapes**

Data suggest organizations that are less mature in their verification processes experience more bugs

© Mentor Graphics Corporation

Men

Source: Wilson Research Group and Mentor Graphics, 2016 Functional Verification Study

20 HF, Demystifying FPGA Design and Verification, STAC 2017

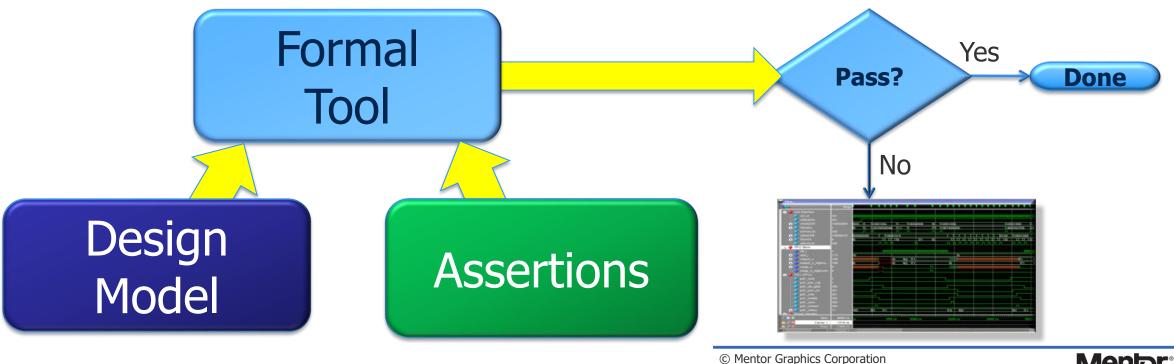

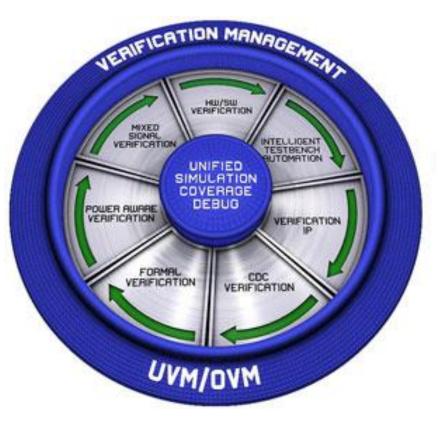

#### **Formal-Based Techniques**

- Does not require a testbench or input stimulus!

- Automatically uses algorithms to verify the functionality

- Verification can be complete

- Complements simulation-based techniques

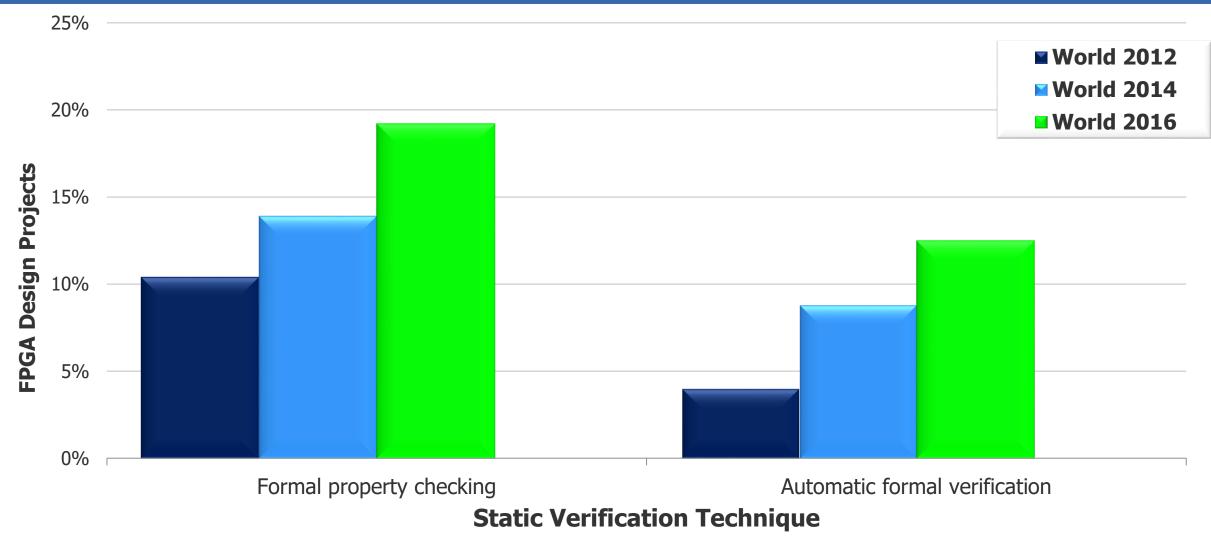

#### **FPGA Formal Technology Adoption Trends**

Source: Wilson Research Group and Mentor Graphics, 2016 Functional Verification Study

#### **Proven Benefits from Advanced Verification**

FPGA customers realize the benefits of evolving their verification methodologies

#### SystemVerilog

Constrained random for better testing

Functional coverage for better insight

• Assertions to improve debug efficiency

UVM

Enables benefits of SystemVerilog

Provides consistent methodology

Promotes reuse for productivity boost

#### Verification IP

- Protocol expertise

- Reduces TB development effort

- Risk reduction

#### FPGA Customer Success Stories

Increased business due to shorter design cycles

400% ROI after adopting UVM and VIP

5 straight FPGA's without a bug

Zero bugs found in lab since moving to UVM

Reduced expensive lab equipment

100x faster to debug vs lab

© Mentor Graphics Corporation

#### www.verificationacadmy.com

### **IMPROVING VERIFICATION SKILLS**

#### **The Most Comprehensive Verification Resource Around**

Free Resource Available to You!

- Online Courses

- Verification Cookbooks

- Discussion Forums

#### Patterns Library

#### **Verification Academy Membership Trend**

Free Resource Available to You!

© Mentor Graphics Corporation

#### WWW.VERIFICATIONACADEMY.COM

## Learn More About Mentor's FPGA Design & Verification Tools and Solutions

Pete LaFauci, Senior Account Manager — Pete\_LaFauci@Mentor.com

- Ted Lin, Technical Account Manager — Ted\_Lin@Mentor.com

- Harry Foster, Chief Scientist Verification

Harry\_Foster@Mentor.com

# A Siemens Business

www.mentor.com